——Dikongsi daripada DWIN Froum

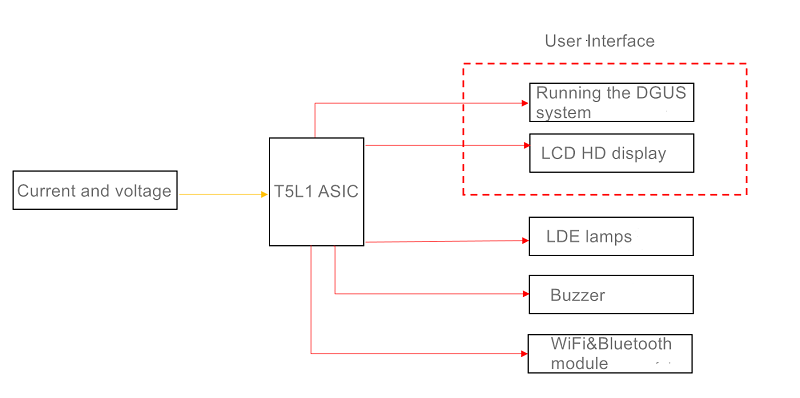

Menggunakan cip DWIN T5L1 sebagai teras kawalan keseluruhan mesin, menerima dan memproses sentuhan, pemerolehan ADC, maklumat kawalan PWM dan memacu skrin LCD 3.5 inci untuk memaparkan status semasa dalam masa nyata.Menyokong pelarasan sentuhan jauh kecerahan sumber cahaya LED melalui modul WiFi, dan menyokong penggera suara.

Ciri-ciri program:

1. Mengguna pakai cip T5L untuk berjalan pada frekuensi tinggi, pensampelan analog AD adalah stabil, dan ralatnya kecil;

2. Sokongan JENIS C disambungkan terus ke PC untuk penyahpepijatan dan pembakaran program;

3. Menyokong antara muka teras OS berkelajuan tinggi, port selari 16bit;Port PWM teras UI, pendahuluan port AD, reka bentuk aplikasi kos rendah, tidak perlu menambah MCU tambahan;

4. Menyokong WiFi, alat kawalan jauh Bluetooth;

5. Menyokong 5~12V DC voltan lebar dan pelbagai input

1.1 Gambarajah skema

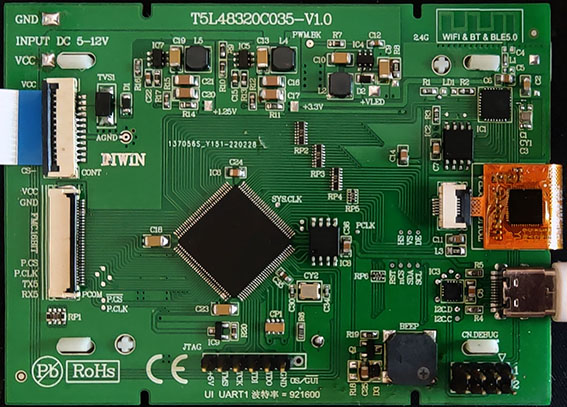

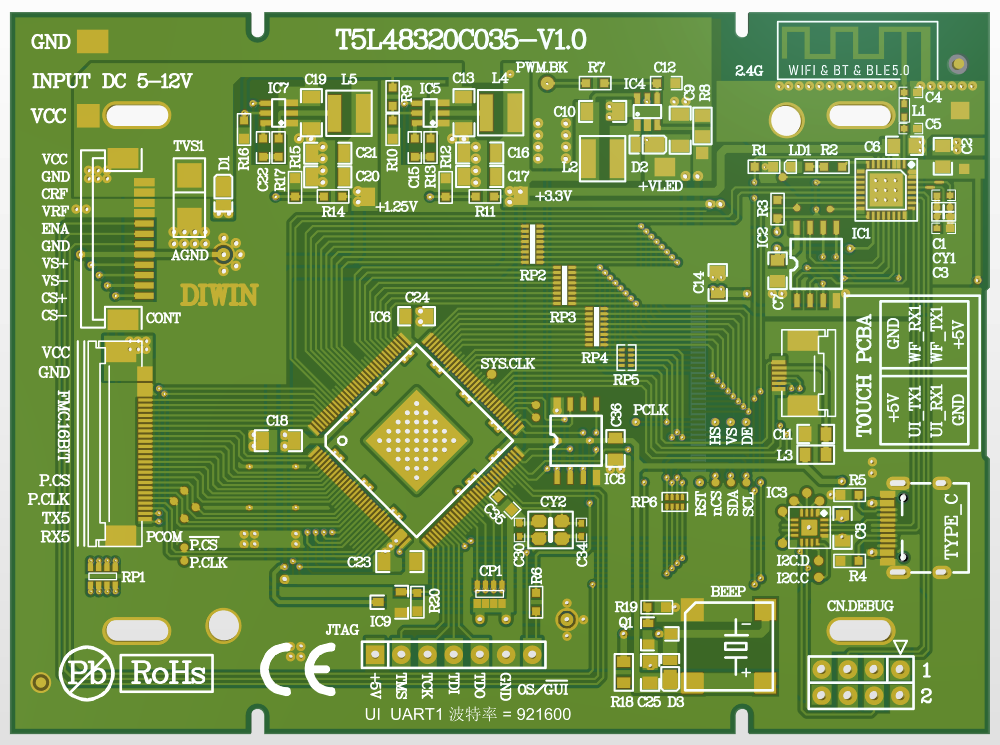

1.2 Papan PCB

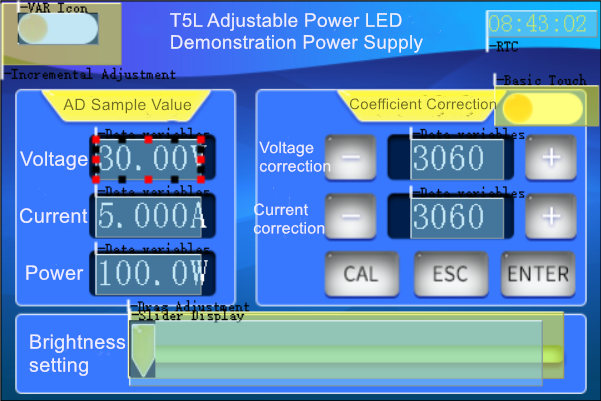

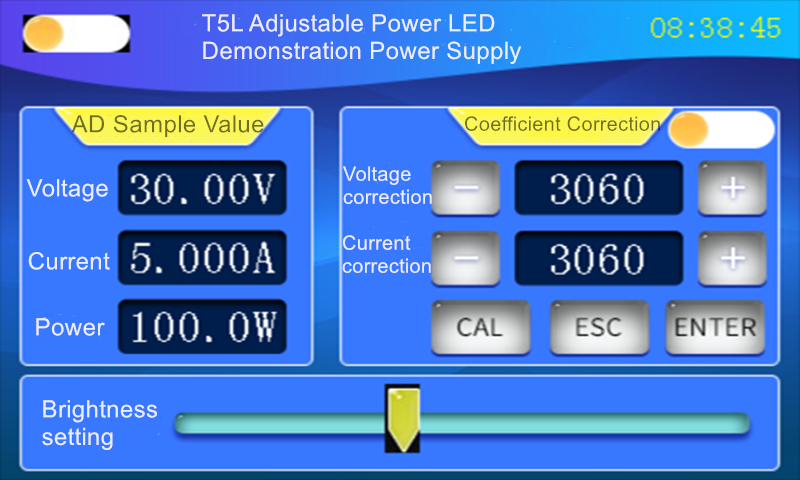

1.3 Antara muka pengguna

pengenalan malu:

(1)Reka bentuk litar perkakasan

1.4 Rajah litar T5L48320C035

1. Bekalan kuasa logik MCU 3.3V: C18, C26, C27, C28, C29, C31, C32, C33;

2. Bekalan kuasa teras MCU 1.25V: C23, C24;

3. Bekalan kuasa analog MCU 3.3V: C35 ialah bekalan kuasa analog untuk MCU.Apabila menaip, tanah teras 1.25V dan tanah logik boleh digabungkan bersama, tetapi tanah analog mesti dipisahkan.Tanah analog dan tanah digital harus dikumpulkan pada kutub negatif pemuat besar keluaran LDO, dan kutub positif analog juga harus dikumpulkan pada kutub positif pemuat besar LDO, supaya Bunyi pensampelan AD diminimumkan.

4. Litar pemerolehan isyarat analog AD: CP1 ialah kapasitor penapis input analog AD.Untuk mengurangkan ralat pensampelan, tanah analog dan tanah digital MCU dipisahkan secara bebas.Kutub negatif CP1 mesti disambungkan ke tanah analog MCU dengan impedans minimum, dan dua kapasitor selari pengayun kristal disambungkan ke tanah analog MCU.

5. Litar buzzer: C25 ialah kapasitor bekalan kuasa untuk buzzer.Buzzer ialah peranti induktif, dan akan terdapat arus puncak semasa operasi.Untuk mengurangkan kemuncak, adalah perlu untuk mengurangkan arus pemacu MOS buzzer untuk menjadikan tiub MOS berfungsi di kawasan linear, dan mereka bentuk litar untuk menjadikannya berfungsi dalam mod suis.Ambil perhatian bahawa R18 harus disambung secara selari pada kedua-dua hujung buzzer untuk melaraskan kualiti bunyi buzzer dan menjadikan buzzer berbunyi segar dan menyenangkan.

6. Litar WiFi: pensampelan cip WiFi ESP32-C, dengan WiFi+Bluetooth+BLE.Pada pendawaian, tanah kuasa RF dan tanah isyarat dipisahkan.

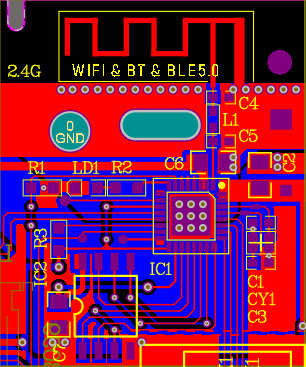

1.5 Reka bentuk litar WiFi

Dalam rajah di atas, bahagian atas salutan kuprum ialah gelung tanah kuasa.Gelung tanah pantulan antena WiFi mesti mempunyai kawasan yang luas ke pembumian kuasa, dan titik pengumpulan pembumian kuasa ialah kutub negatif C6.Arus yang dipantulkan perlu disediakan di antara pembumian kuasa dan antena WiFi, jadi mesti ada salutan tembaga di bawah antena WiFi.Panjang salutan tembaga melebihi panjang sambungan antena WiFi, dan sambungan akan meningkatkan sensitiviti WiFi;titik pada kutub negatif C2.Kawasan kuprum yang besar boleh melindungi bunyi yang disebabkan oleh sinaran antena WiFi.2 alasan tembaga diasingkan pada lapisan bawah dan dikumpulkan ke pad tengah ESP32-C melalui vias.Pembumian kuasa RF memerlukan impedans yang lebih rendah daripada gelung pembumian isyarat, jadi terdapat 6 vias dari pembumian kuasa ke pad cip untuk memastikan galangan yang cukup rendah.Gelung tanah pengayun kristal tidak boleh mempunyai kuasa RF yang mengalir melaluinya, jika tidak, pengayun kristal akan menjana jitter frekuensi, dan mengimbangi frekuensi WiFi tidak akan dapat menghantar dan menerima data.

7. Litar bekalan kuasa LED lampu latar: Persampelan cip pemacu SOT23-6LED.Bekalan kuasa DC/DC ke LED secara bebas membentuk gelung, dan tanah DC/DC disambungkan ke tanah LOD 3.3V.Memandangkan teras port PWM2 telah dikhususkan, ia mengeluarkan isyarat PWM 600K, dan RC ditambah untuk menggunakan output PWM sebagai kawalan ON/OFF.

8. Julat input voltan: dua langkah turun DC/DC direka bentuk.Ambil perhatian bahawa perintang R13 dan R17 dalam litar DC/DC tidak boleh ditinggalkan.Dua cip DC/DC menyokong input sehingga 18V, yang sesuai untuk bekalan kuasa luaran.

9. Port nyahpepijat USB JENIS C: JENIS C boleh dipasang dan dicabut ke hadapan dan ke belakang.Sisipan ke hadapan berkomunikasi dengan cip WIFI ESP32-C untuk memprogramkan cip WIFI;sisipan terbalik berkomunikasi dengan XR21V1410IL16 untuk memprogramkan T5L.JENIS C menyokong bekalan kuasa 5V.

10. Komunikasi port selari: Teras OS T5L mempunyai banyak port IO percuma, dan komunikasi port selari 16bit boleh direka bentuk.Digabungkan dengan protokol port selari ST ARM FMC, ia menyokong baca dan tulis segerak.

11. Reka bentuk antara muka berkelajuan tinggi LCM RGB: Output T5L RGB disambungkan terus ke LCM RGB, dan rintangan penampan ditambah di tengah untuk mengurangkan gangguan riak air LCM.Apabila pendawaian, kurangkan panjang sambungan antara muka RGB, terutamanya isyarat PCLK, dan tingkatkan mata ujian antara muka RGB PCLK, HS, VS, DE;port SPI skrin disambungkan ke port P2.4~P2.7 T5L, yang mudah untuk mereka bentuk pemacu skrin.Pimpin mata ujian RST, nCS, SDA, SCI untuk memudahkan pembangunan perisian asas.

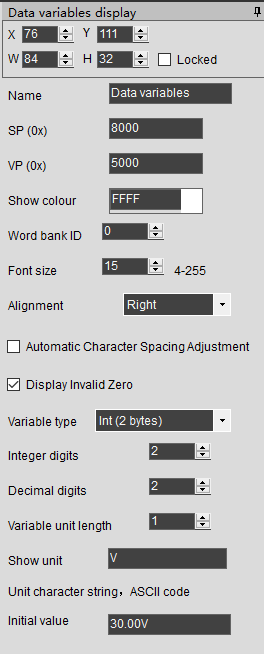

(2) Antara muka DGUS

1.6 Kawalan paparan pembolehubah data

(3) OS

//———————————Format baca dan tulis DGUS

struct typedef

{

u16 addr;//Alamat pembolehubah UI 16bit

u8 datLen;//panjang 8bitdata

u8 *pBuf;// 8bit penunjuk data

} UI_packTypeDef;// DGUS membaca dan menulis paket

//——————————-kawalan paparan pembolehubah data

struct typedef

{

u16 VP;

u16 X;

u16 Y;

u16 Warna;

u8 Lib_ID;

u8 Saiz Fon;

u8 Penjajaran;

u8 IntNum;

u8 DecNom;

u8 Jenis;

u8 LenUint;

u8 StringUinit[11];

} Number_spTypeDef;//struktur penerangan pembolehubah data

struct typedef

{

Number_spTypeDef sp;//takrifkan penunjuk perihalan SP

UI_packTypeDef spPack;//define SP pembolehubah DGUS baca dan tulis pakej

UI_packTypeDef vpPack;//define vp variable DGUS read and write pakej

} Number_HandleTypeDef;//struktur pembolehubah data

Dengan definisi pemegang pembolehubah data sebelumnya.Seterusnya, tentukan pembolehubah untuk paparan pensampelan voltan:

Number_HandleTypeDef Hsample;

u16 voltan_sampel;

Pertama, laksanakan fungsi permulaan

NumberSP_Init(&Hsample,voltage_sample,0×8000);//0×8000 di sini ialah penunjuk penerangan

//——Pembolehubah data menunjukkan permulaan struktur penunjuk SP——

batalkan NumberSP_Init(Number_HandleTypeDef *nombor,u8 *nilai, u16 numberAddr)

{

nombor->spPack.addr = numberAddr;

nombor->spPack.datLen = saiz(nombor->sp);

nombor->spPack.pBuf = (u8 *)&nombor->sp;

Read_Dgus(&nombor->spPack);

nombor->vpPack.addr = nombor->sp.VP;

suis(number->sp.Type) //Panjang data pembolehubah vp dipilih secara automatik mengikut jenis pembolehubah data yang direka dalam antara muka DGUS.

{

kes 0:

kes 5:

nombor->vpPack.datLen = 2;

pecah;

kes 1:

kes 2:

kes 3:

kes 6:

nombor->vpPack.datLen = 4;

kes 4:

nombor->vpPack.datLen = 8;

pecah;

}

nombor->vpPack.pBuf = nilai;

}

Selepas pemulaan, Hsample.sp ialah penunjuk perihalan pembolehubah data pensampelan voltan;Hsample.spPack ialah penunjuk komunikasi antara teras OS dan pembolehubah data pensampelan voltan UI melalui fungsi antara muka DGUS;Hsample.vpPack ialah atribut menukar pembolehubah data pensampelan voltan, seperti Warna fon, dll. juga dihantar ke teras UI melalui fungsi antara muka DGUS.Hsample.vpPack.addr ialah alamat pembolehubah data pensampelan voltan, yang telah diperoleh secara automatik daripada fungsi permulaan.Apabila anda menukar alamat pembolehubah atau jenis data pembolehubah dalam antara muka DGUS, tidak perlu mengemas kini alamat pembolehubah dalam teras OS secara serentak.Selepas teras OS mengira pembolehubah voltage_sample, ia hanya perlu melaksanakan fungsi Write_Dgus(&Hsample.vpPack) untuk mengemas kininya.Tidak perlu membungkus voltan_sample untuk penghantaran DGUS.

Masa siaran: Jun-15-2022